ThreadX Porting van minuscuul OS naar RISC-V

ThreadX is een vederlicht realtime besturingssysteem (RTOS) voor veeleisende embedded systemen en IoT-apparaten. Het is wereldwijd meer dan zes miljard keer geïnstalleerd, onder meer in consumentenapparatuur, medische elektronica en industriële machines. Technolution Advance realiseerde een port van ThreadX naar een commercieel beschikbare RISC-V-softcoreprocessor

Klein en veelzijdig RTOS

ThreadX wordt geproduceerd door Express Logic, marktleider op het gebied van royaltyvrije realtime besturingssystemen. De basisversie van ThreadX is minuscuul: het RTOS is maar twee kilobyte groot en heeft niet meer dan een kilobyte geheugenruimte nodig. Hierdoor is ThreadX geschikt voor toepassingen met beperkte resources en een laag energieverbruik. RTOS wordt dan ook veel toegepast in IoT-apparaten. Het systeem is klein maar veelzijdig: het is een kernel die onder meer kan worden ingezet om threads te schedulen, interrupts af te handelen en te communiceren tussen threads. De basisfunctionaliteit van ThreadX kan eenvoudig worden uitgebreid.

Port naar RISC-V

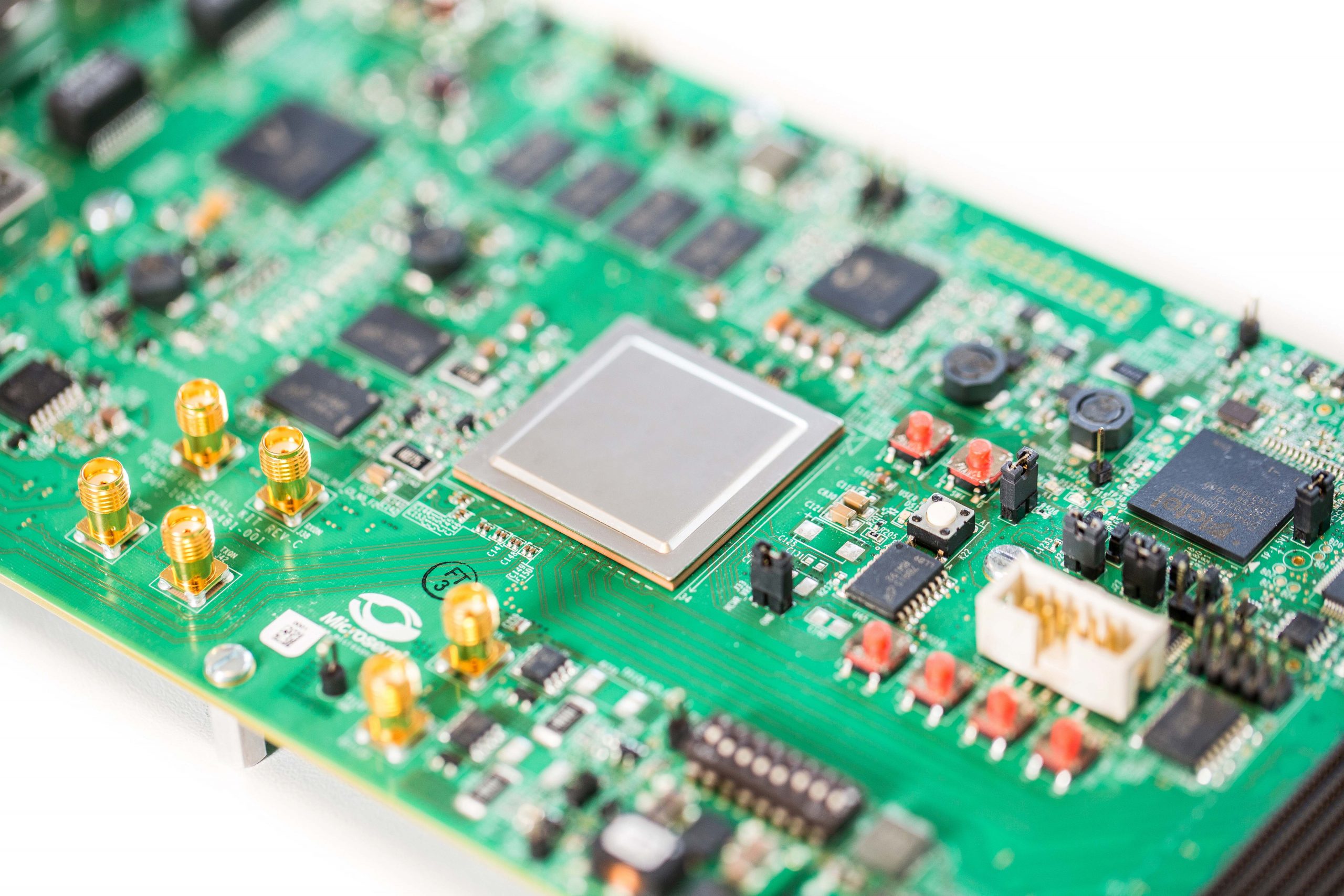

Express Logic vroeg ons of het mogelijk was om ThreadX te implementeren in een RISC-V-processor van Microsemi. RISC-V is een opensource-instructieset, waarvoor zowel softcores als fysieke processors kunnen worden ontwikkeld. Een RISC-V-softcoreprocessor kan vervolgens worden geïmplementeerd op een FPGA, een programmeerbare chip. Technolution Advance ontwikkelde al eerder een RISC-V-processor als basis voor securityproducten. Met deze port van ThreadX biedt Express Logic nu een kant-en-klaar RTOS voor de RISC-V-architectuur dat eenvoudig kan worden geïmplementeerd op een FPGA. Voor ontwikkelaars die gebruikmaken van softcores is ThreadX een aantrekkelijke optie